יש עוד קצת מיץ בלימון הזה - חלק שני

בחלק הראשון של הפוסט דיברנו על איך עוד ניתן לסחוט את הלימון של חוק מור ולהגביר את צפיפות הטרנזיסטורים ליחידת שטח. סקרנו את ההיסטוריה של מבני הטרנזיסטור ודיברנו על הדבר הגדול הבא – הGAA שעתיד להכנס לתהליכי הייצור החדשים – N2 של TSMC וה-18A של אינטל. אם לא קראתם, מוזמנים לגלול אחורה ולקרוא. היום נעסוק בדרך השניה שתאפשר לנו לצופף עוד קצת את הטרנזיסטורים על הסיליקון, והוא מגיע ממקום לא צפוי. החיבוריות שבין הטרנזיסטורים עצמם. חלק שני בסדרה.

ממשיכים לסחוט את הלימון של חוק מור ולהוציא עוד קצת מיץ בשביל הסלט של צפיפות הטרנזיסטורים בטכנולוגיות הייצור החדשות של המוליכים למחצה.

הפעם, נדבר על איך אפשר לאפשר חיבוריות חכמה יותר בין כל הטרנזיסטורים האלה כך שנוכל לצופף אותם עוד טיפה. על מה מתבזבזים היום, אפילו בתהליכי הייצור החדשים ביותר שטחי סיליקון יקרים ואיך אפשר בכל זאת להמנע מזה.

בפוסט הקודם בסדרה הזכרנו שההשפעה על שטח הסיליקון שתופס צ'יפ יחיד (תחת דיזיין זהה) מושפעת מארבעה גורמים עיקריים:

גודל התאים עצמם (כל תא מורכב ממספר טרנזיסטורים).

משאבי החיווט

גודל וכמות זכרונות ה-SRAM (יחידות זיכרון הנמצאות בתוך השבב).

גודל וכמות החלקים האנלוגיים (בעיקר יחידות קישוריות אל העולם החיצון).

הפוסט הקודם התמקד בגודל התאים, עתה נדון כיצד משאבי החיווט משפיעים על צפיפות התאים הכוללת.

המבנה הרב-שכבתי של שבב הסיליקון

בשבב מודרני יהיו כמליוני ואפילו מיליארדי טרנזיסטורים. כל אחד ואחד מהטרנזיסטורים הללו, המרכיבים תאים לוגיים, חייב להיות מחובר לחשמל בצורה מסוימת. המשמעות היא שלכל אחד ואחד מהטרנזיסטורים האלה צריך להיות חיבוריות ישירה לחשמל. איך נחבר כל אחד מהם לחשמל? הרי כמו שאמרנו, יש מיליארדים מהם. כדי להבין את זה, צריך להבין את המבנה של השבב.

שבב הסיליקון בנוי מ2 חלקים אשר מונחים אחד מעל השני, כאשר כל אחד מהחלקים הללו מורכב ממספר שכבות.

החלק התחתון של הסיליקון, המכונה גם Backend, הוא החלק בו מוטמעים הטרנזיסטורים עצמם. בחלק זה תוכלו למצוא את הסיליקון חלקי הטרנזיסטור השונים (source, drain, gate ו-bulk) התעלות בהן זורם הזרם החשמל והחיבוריות הבסיסית ביותר בין הטרנזיסטורים אשר מרכיבות יחד את התא הלוגי.

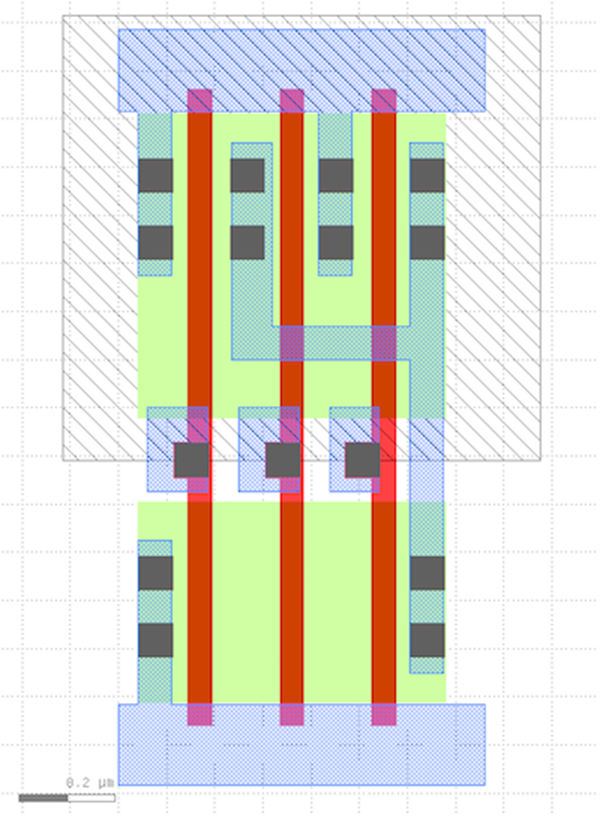

בתמונה – שרטוט של מבנה פיזיקלי של תא לוגי מסוג NAND3. כל צבע מתאר שכבה אחרת מהבסיס ועד שכבת המתכת הנקראת M1 של פיני הסיגנל/מתח של התא.

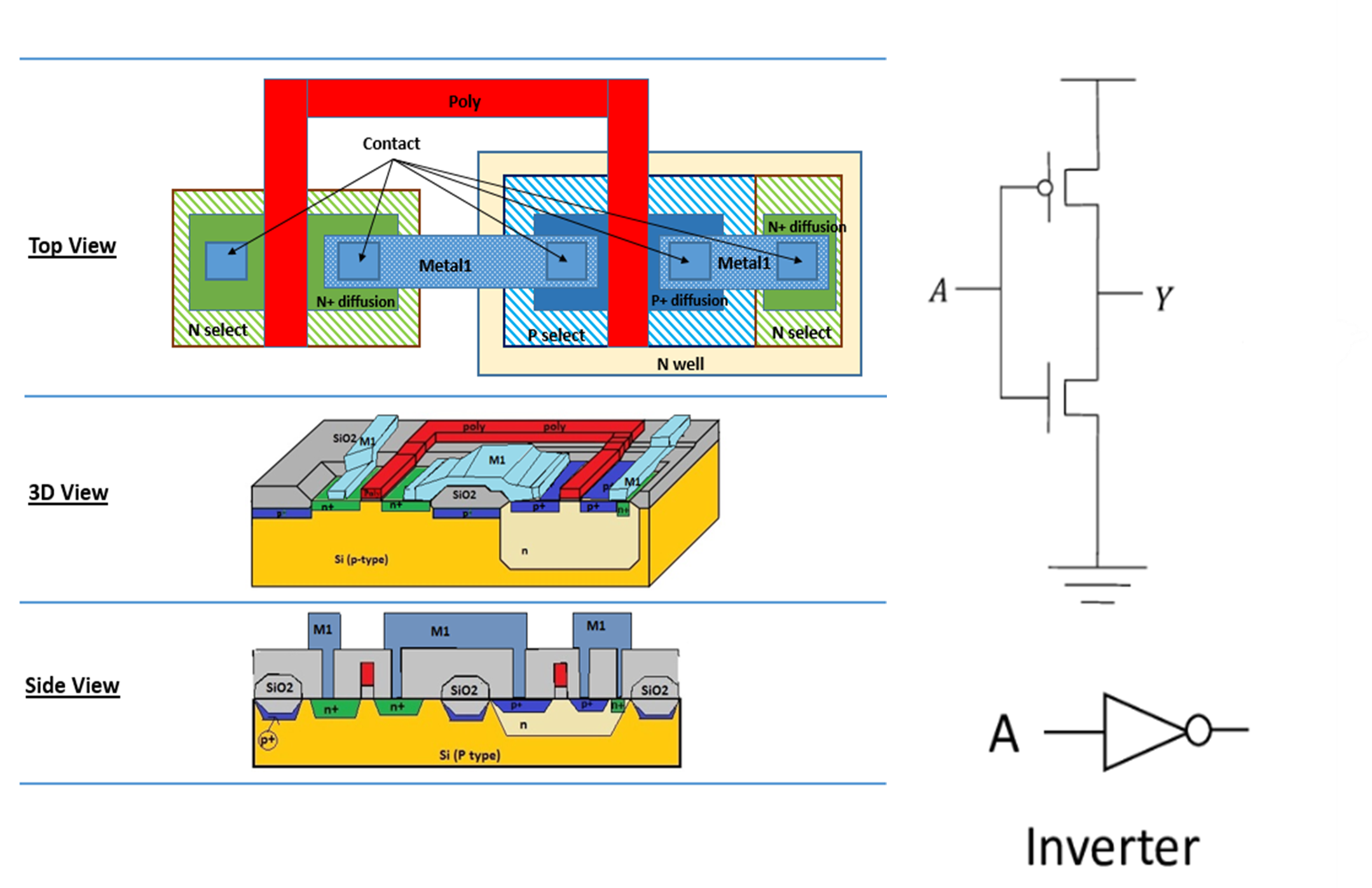

לדוגמה, תא המממש את הפונקציה הלוגית הפשוטה ביותר, NOT (נקרא גם אינוורטר – מהפך), יהיה מורכב מ2 טרנזיסטורים המחוברים יחדיו בקונפיגורציה מסוימת כך שכל סיגנל חשמלי הנכנס אליו דרך פין הכניסה, ופוגש את ה-gate של הטרנזיסטורים, יצא מהופך מפין המוצא של התא. באופן סכמטי זה נראה כמו בתמונה מטה. בסיליקון, חלקי הטרנזיסטורים למשל יהיו בשכבות מסוימות והחיבוריות ביניהן תמצא בשכבה נפרדת. הקשר של התא אל העולם החיצון יהיה באמצעות פיני הכניסה והיציאה שלו, החשופים בשכבה אחד מעל להכל – השכבה הנמוכה ביותר מבין שכבות הFrontend. כך גם פיני אספקת המתח והאדמה.

חלק הFrontend של הסיליקון מורכב מממספר שכבות (בפרוססים מתקדמים מספר שכבות המתכת הללו נע בין 12 ל18 שכבות, כתלות בפרוסס ובבחירה של הלקוח) דרכן מחוברים התאים הלוגיים. כל שכבה ממוספרת מ0 (מסומן M0) עד שכבות גבות כמו M17. דרך כל שכבה כזו, תחת חוקיות מסוימת הנקבעת ע"י היצרן (נקרא DRC למי שמעוניין או מעוניינת להעמיק), נוכל לחבר את התאים הלוגיים אחד לשני ולבנות את המעגל החשמלי.

מעל לחלק הפרונטאנד נמצאים רכיבים הנקראים באמפים (bumps) המוליכים אספקת חשמל מהעולם החיצון (מהכרטיס דרך האריזה בתוכה ממוקם השבב) אל תוך הצ'יפ. הבאמפים מתחברים אל שכבות הפרונטאנד והחשמל מולך אל התאים באמצעות רשת חשמל הפרוסה משכבת המתכת הגבוהה ביותר ועד הנמוכה ביותר.

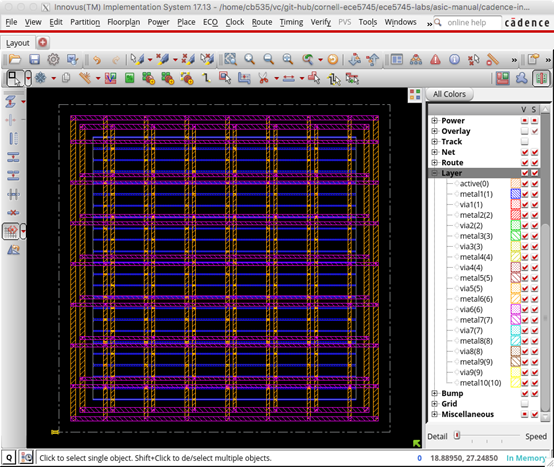

בתמונה – רשת הובלת הספק (נקראת Power Grid או PDN – Power Delivery Network). כל צבע מתאר שכבת מתכת אחרת

בנוסף לרשת החשמל, עלינו לחבר את התאים הלוגיים אל המעגל החשמלי אותו אנו מעוניינים לממש. זאת אומרת, למהפך הפשוט שהצגנו קודם יש 4 פינים – 2 לאספקת מתח/אדמה ועוד 2 כניסה/מוצא לוגיים.

אם כך, על גבי שבב יהיו 2 סוגים של חיבוריות – אספקת מתח/אדמה וסיגנל (המחולק בתוכו לסיגנל פשוט או שעון – אבל לא נגע בזה כאן).

כלומר, מעגל המשלב בתוכו כמיליארדי טרנזיסטורים שצריכים להיות מחוברים אחד לשני בקונפיגורציה מסוימת ידרוש חיבוריות מסובכת וענפה, אחת של אספקת המתח לכלל התאים והשנייה בין הטרנזיסטורים לצורך העברת מידע. כל החוטים המחברים את התאים זה לזה ומוליכים את זרם האספקה צריכים להיות מוכלים על גבי מספר שכבות הFE - כאשר אין מקום לחיבוריות מידע בשכבה אחת, נעבור לשכבה מעל וכך הלאה, כשאנו מאכלסים את כל השכבות בחיבוריות בין הטרנזיסטורים ומממשים את המעגל החשמלי אותו תיכננו. נשמע לכם/ן כמו בלגן רציני? זה אכן בלגן רציני.

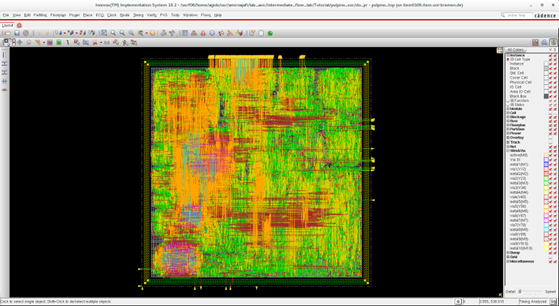

בתמונה – חיבוריות של יחידה אחת (נחשבת פשוטה במיוחד) מתוך שבב. כל צבע מתאר שכבה אחרת.

תחרות על משאבי החיווט

גם רשת הPDN תופסת משאבי חיווט, זאת אומרת, היכן שעובר קו אספקה לתאים לא יכול להיות מחווט קו של סיגנל מידע. ככל שיש לנו יותר קוי אספקה, כך יש לנו פחות מקום לחיווט של מתכות המוליכות סיגנלים, ולהפך. אז פתרון אחד יהיה פשוט לחווט פחות קווי אספקה, מה שעשוי להוביל לנפילות מתח גדולות מידי על התאים (בגלל מרחק גדול מהbump הקרוב והתנגדות גדולה מידי) ולשגיאות של ממש בפעולתו הלוגית של השבב (כתוצאה מIR Drop – לא נגע בזה כאן). מצד שני, לעיתים, בשל אותה הסיבה, נהיה חייבים לעבות את רשת ה-PDN באזורים מסוימים בצ'יפ על מנת לחזק את הובלת זרם האספקה – מה שיגרור קושי בחיווט המידע.

דבר נוסף וחשוב יותר שכדאי לשים אליו לב, שבכל מקום בו צפיפות התאים תהיה גבוהה יותר, פוטנציאל צפיפות החוטים תהיה גבוהה יותר ואנו עשויים לקבל תוצאה שנקראת Congestion – זוהי צפיפות חוטים גבוהה כ"כ שלא ניתן כלל לחבר את התאים זה לזה (תחת מגבלות נוספות ושונות הדרושות לכך שהצ'יפ יתפקד – טיימינג, IR Drop). הפתרון הנפוץ ביותר לבעיה כזו, בשלבים המוקדמים, יהיה מיקום מחדש של תאים שמוקמו באזורים בהם יש פוטנציאל גבוה לcongestion באזורים אחרים, בהם קיימת סכנה נמוכה יותר לcongestion, כך שיחד איתם תנוע גם החיבוריות אליהם ויופחת עומס החיווט באזור. באופן זה, ובצורה קצת אבסורדית, כלי הדיזיין ידאגו לכך שהאזורים עם ה-congestion הגבוה ביותר יהיו צפופים פחות בתאים לוגיים מהאזורים האחרים כך שנקבל קורלציה הפוכה בין צפיפות תאים לצפיפות חוטים.

דבר זה מגביל את כמות התאים הקומבינטורים שנוכל להכניס לתא שטח אחד, כלומר, אם היו לנו יותר משאבי חיווט, היינו יכולים להכניס יותר תאים קומבינטורים לתא שטח נתון ובכך להקטין סך הכל את גודלו של הצ'יפ שלנו. בכך בעצם באופן עקיף זמינות משאבי החיווט משפיעה על גודלו של השבב.

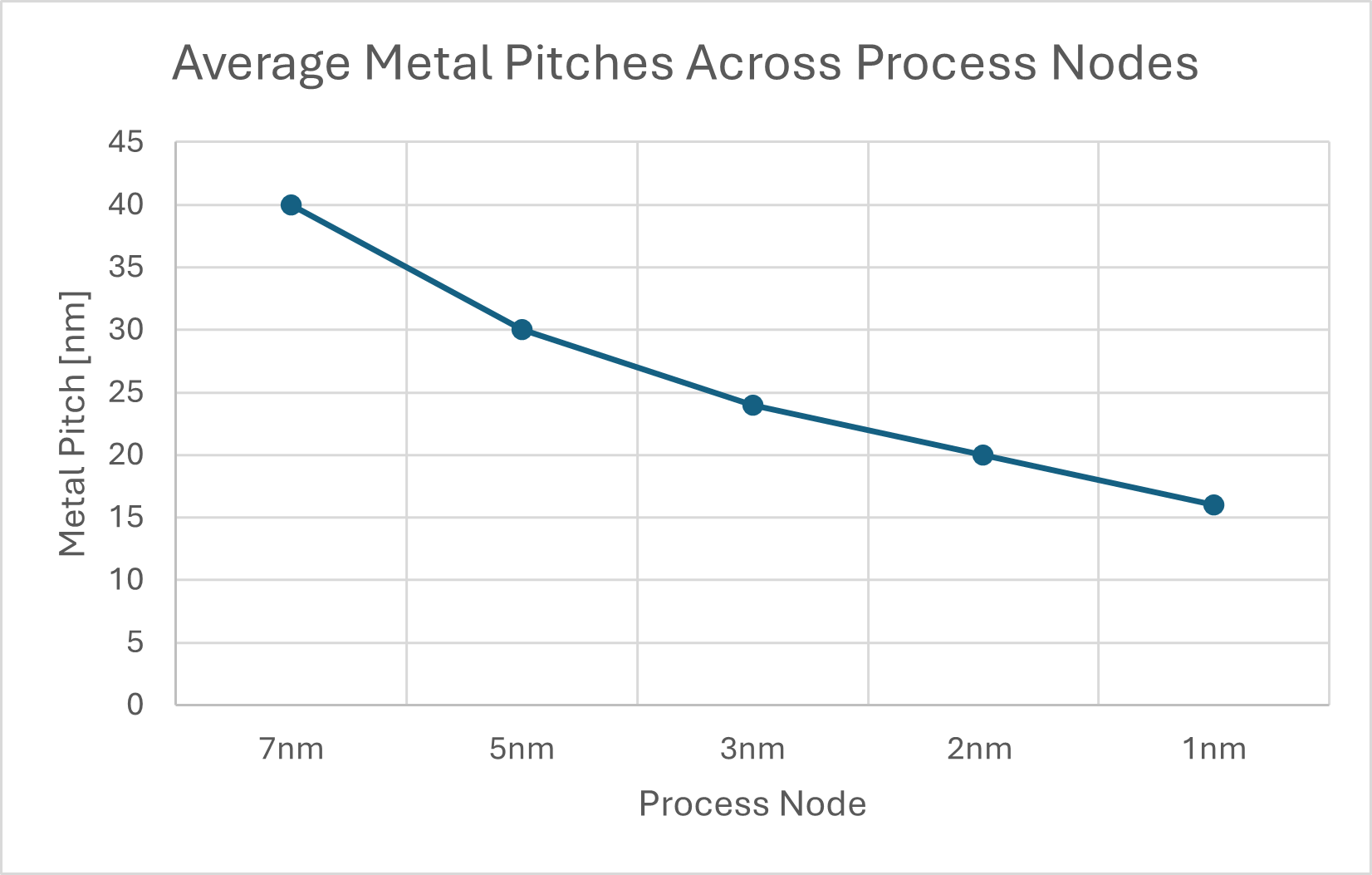

בתמונה – הpitch הממוצע בכל טכנולוגיה. ניתן לראות שקצב המיזעור הולך ומאט (נתונים – ויקיפדיה).

קווי המתח עוברים מתחת לאדמה –

אז היינו מצפים שבין דור לדור המרחק בין כל צמד חוטים (נקרא גם pitch) העובר בשכבה מסוימת יקטן וכן עובי כל חוט כזה יתעבה. אולם, גם כאן הטכנולוגיה נתקלת בקיר וקצב הקטנת הpitch בכל השכבות איטי ממה שהיינו רוצים.

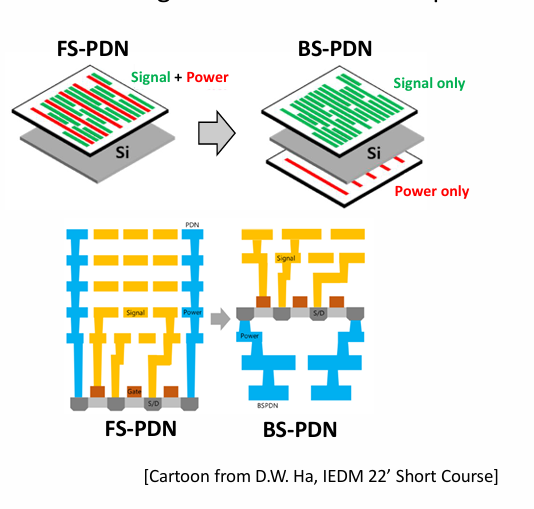

אז מה אפשר לעשות? ממש כמו שהיינו רוצים שיהיה אצלנו בשכונה, אחד הפתרונות שמציעים הפרוססים המתקדמים ביותר היום הואNetwork Backside Power Delivery (או בקיצור BSPDN) שמשמעותו הולכת זרם אספקה דווקא מלמטה, מחלק הBE של הסיליקון ולא ה-FE. אם נצליח לעשות דבר שכזה, הרי שנפנה כמויות אדירות של משאבי חיווט לטובת חיבוריות של מידע וכך נוכל לקרב עוד יותר את התאים זה לזה ולהגדיל את הצפיפות – מה שיעמוד בתיאום עם חוק מור ונוכל לנשום לרווחה לעוד שנתיים (אולי). אבל קיימות מספר בעיות:

אספקת המתח מגיעהמהבאמפים שנמצאים בשכבה העליונה ביותר של חלק הFE

הפינים האחראים על קבלת זרם האספקה נמצאים בשכבת ה-FE

קיים סיכון מסחרי לא מבוטל – שימוש בשיטה הזו עשוי להוריד את הYield (אחוז השבבים הטובים למכירה מתוך כלל השבבים המיוצרים).

מורכבות גבוהה מאוד בייצור.

אלו חלק מהסיבות שה-Foundries (Intel, TSMC, Samsung ועוד) דחיינו את הטמעת הטכנולוגיה הזו, עד שכבר לא נותרה ברירה.

בתמונה – המחשה של העברת הPDN לחלק האחורי של השבב.

כל אחד מה-Foundries מציעה פתרון מעט שונה למימוש של BSPDN, כאשר לכל אחד מהם יתרונות וחסרונות על האחרים. אחד הפתרונות היותר מפורסמים הוא הPowerVia של אינטל, אותו הם מטמיעים בטכנולוגיית ה-18A שלהם. גם TSMC תכניס את טכנולוגיית ה-BSPDN לתהליך הייצור 16A שלה.

נראה שמרגע שיצליחו היצרנים להטמיע את הטכנולוגיה הזו ולהפיק yield גבוה ביצור המוני, הBSPDN כאן כדי להשאר.

אם יהיה ביקוש, אעשה בעתיד פוסט על סוגי הBSPDN הקיימים ועל ההבדלים ביניהם.

לסיכום –

לא הייתי אומר שיש עוד הרבה אסים בשרוול, אבל האנושות מצליחה לחלוב עוד טיפה את הפרה הזאת של חוק מור. ייתכן והדור הבא של הפרוססים כבר יאלץ אותנו להפרד, לפחות חלקית, מהסיליקון המוכר והאהוב ולעבור לחומרים אחרים ולמבני טרנזיסטורים שונים. עד אז, קנתה האנושות עוד כמה שנים בהם היא יכולה לטפוח לעצמה על השכם ולהגיד שחוק מור חי. האמת? מרשים.