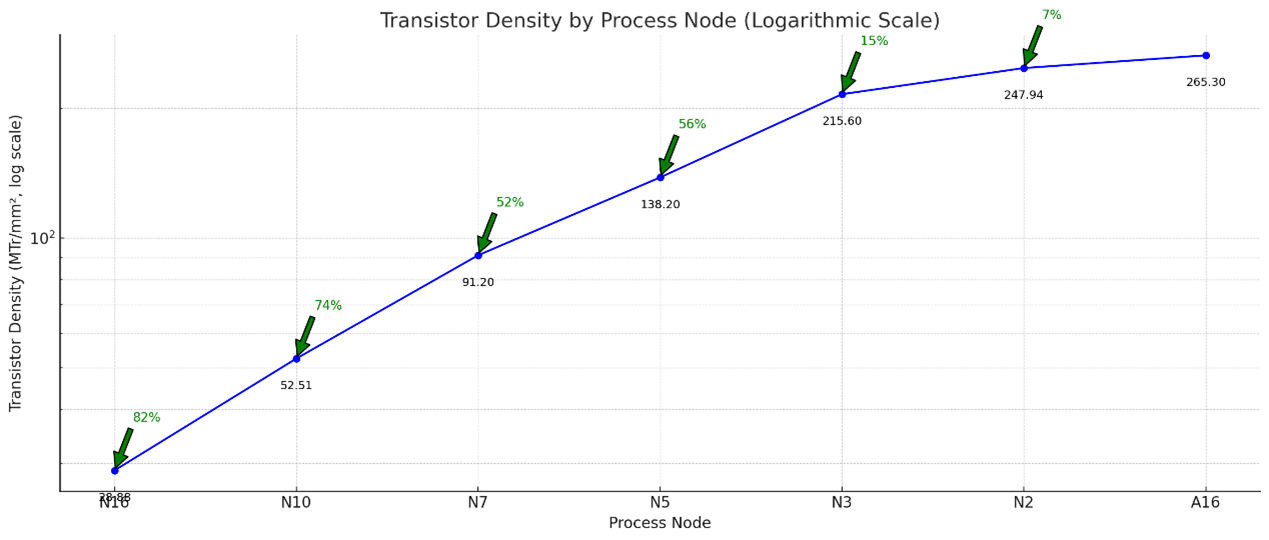

אז את תהליכי הייצור (Process Nodes) – 2 ננומטר, 3 ננומטר, 5 ו7 כולנו מכירים. ככל שתהליך הייצור (הפרוסס) מתקדם יותר, כך עלותו גבוהה יותר ותהליך הפיתוח עבורו מורכב יותר. יחד עם זאת, מגיעים יתרונות במונחים של ביצועים, הספק ושטח – בהתאם לחוק מור, ניתן לדחוס יותר טרנזיסטורים על צ'יפ יחיד.

אך בשנים האחרונות, מגמת השיפור בין פרוסס לפרוסס הלכה וקטנה. יתרונות ההספק והביצועים שמספקים פרוססים חדשים כבר לא כמו פעם, ומעל הכל, דחיסות הטרנזיסטורים כבר לא משתפרת באותו הקצב. לכן הפך להיות משתלם פחות ופחות לחברות לעבור לפרוססים המתקדמים ביותר, ובלית הכרח, חלקן החליטו להשאר עם הותיקים והמוכחים. אז האם מדובר כאן על סופו של חוק מור?

אולי, אבל גם אולי לא – בזכות הטכנולוגיה שג'נסן מדבר עליה.

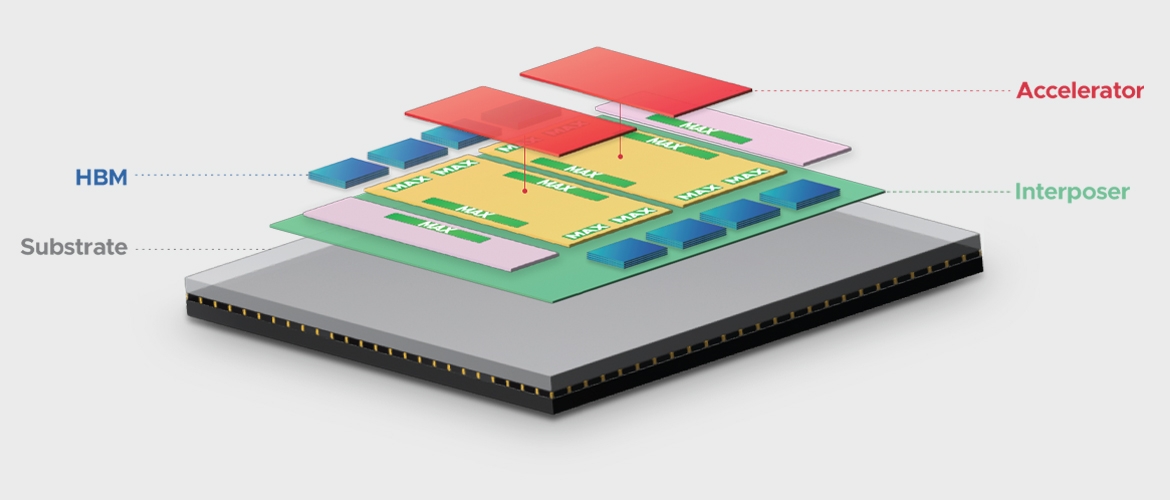

בתמונה – צפיפות הטרנזיסטורים בטכנולוגיות של TSMC כאשר השמאלית היא הישנה ביותר. בירוק אחוזי השיפור מהדור הקודם.

מה עשינו עד היום?

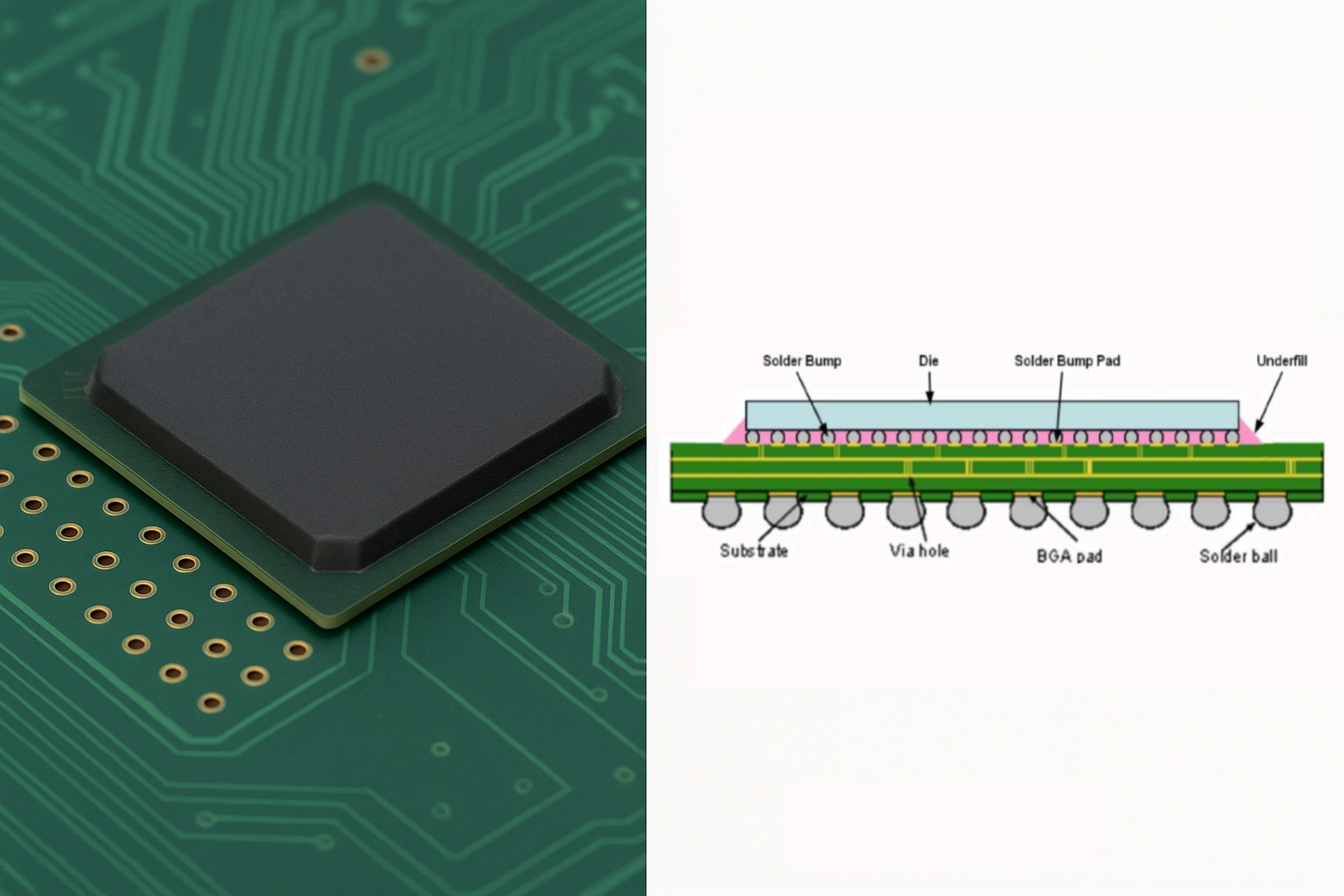

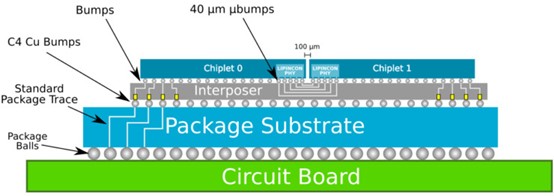

כששבב מיוצר ונחתך מתוך פיסת הסיליקון (וייפר) הוא מוצב בתוך אריזה. האריזה אחראית על קישוריותו של השבב אל העולם החיצון ומגנה עליו מפני פגעים כאלה או אחרים. בצורה הזו כשנופל לכם הסלולרי או הלפטופ, אם לא הייתם לגמרי חסרי מזל, הוא לא נהרס. בתמונה, מה שקורה בתוך טכנולוגיית אריזה מסורתית והחיבוריות של זה לבורד.

אם לא נצטמצם, נתרחב -

בעבר, זו הייתה המשמעות המרכזית של האריזה (הPackage-), אך בשנים האחרונות, בשל ההתקדמות איטית בציר הפרוססים, ועליית הדרישה לכוח מיחשוב, ענקיות הייצור באו עם פתרון חדש – ה-Multi-Die. מספר שבבים הארוזים יחדיו באותו ה-Package ומקושרים ביניהם.

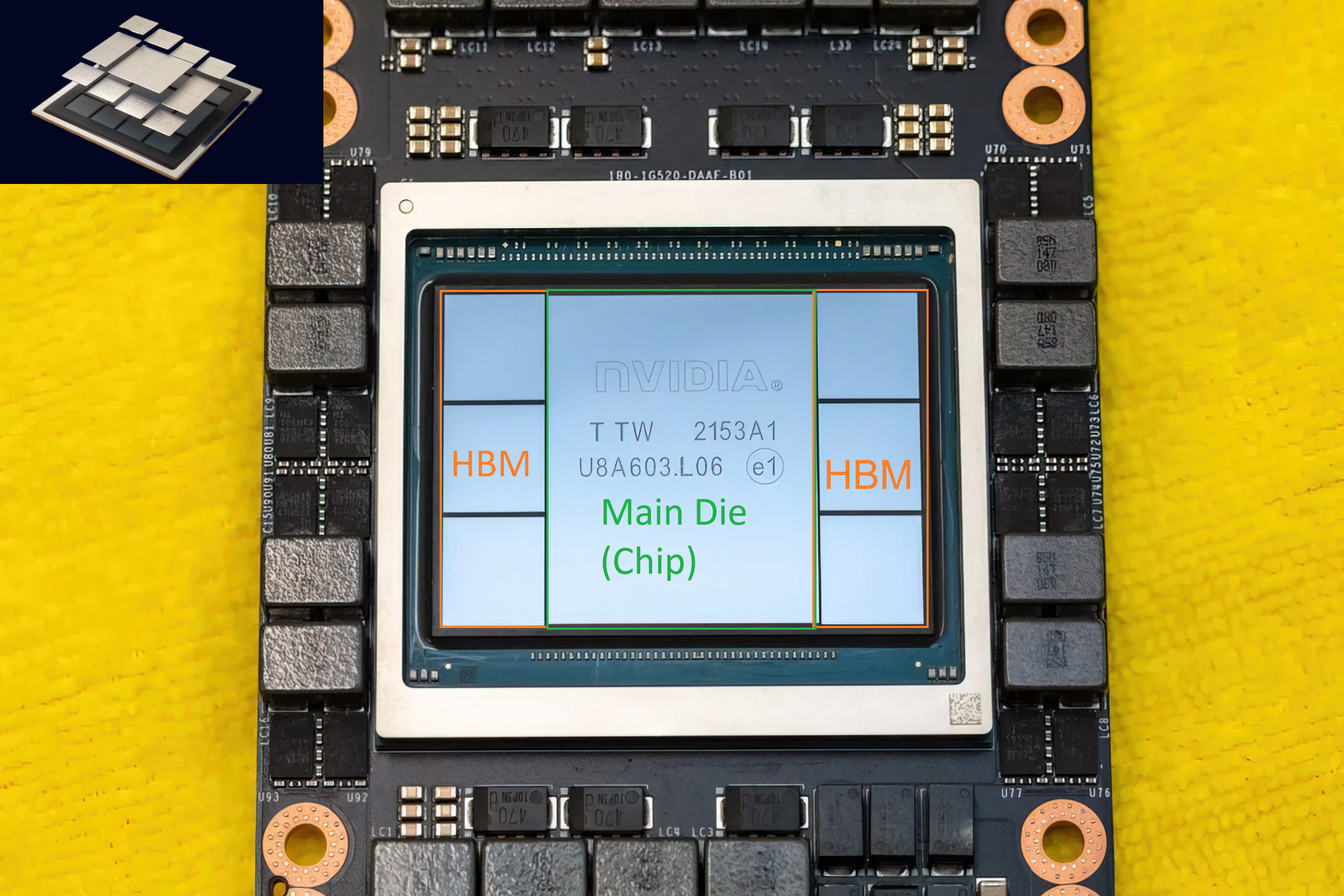

השבבים הללו אפילו לא חייבים להיות עשויים מתוך אותו תהליך ייצור, בהחלט ייתכן שמספר מסוים מהשבבים יהיו מטכנולוגיית 7 ננומטר ואחרים יהיו מ3 ננומטר. בנוסף, ניתן גם להכניס זיכרון יחד לאותה האריזה – HBM (High Bandwidth Memory) ובכך לחסוך את זמן המעבר בין השבב אל הזיכרון ולהגדיל סך רוחב הפס – זאת במקום זכרונות שהיו מוצבים במרחק גדול יותר על אותו הבורד יחד עם השבב.

היתרונות והחזון -

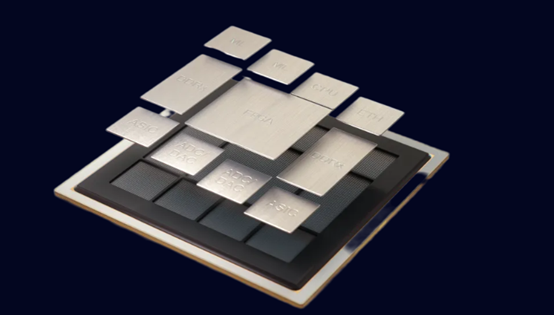

טכנולוגיות הMulti-Die מאפשרות לאנוודיה (ושאר החברות) לארוז שבבים מפרוססים שונים ובכך להגדיל את אחוז השבבים העומדים בבדיקות לפני השיווק ללקוח (נקרא גם Yield) , מאפשרות למחזר שבבים ולמקם יחד עם שבבים חדשים ואפילו ישנן חברות שבחזונן רואות חברות קטנות מאוד ואפילו משתמשים פרטיים מרכיבים כמו אבני לגו שבבים מסוגים שונים אל תוך אריזה אחת ובכך מייצרים מוצרי חומרה אמיתיים, חדשים ומגניבים, ללא הצורך להשקיע עשרות ואפילו מאות מיליוני דולרים בייצור ואריזה. תמונה – מתוך האתר של אחת מחברות החזון Zero ASIC.

הזוכה הגדולה -

ספקיות הטכנולוגיה העיקריות של הMulti-Die הן איך לא, TSMC, אינטל וסמסונג. בנוסף, קיימות חברות צד שלישי (OSAT) כמו ASE הטייוואנית וAmkor הדרום קוריאנית בעלות טכנולוגיות קנייניות אחרות עם יתרונות וחסרונות, המאפשרות לשבץ יחדיו שבבים על אותה האריזה.

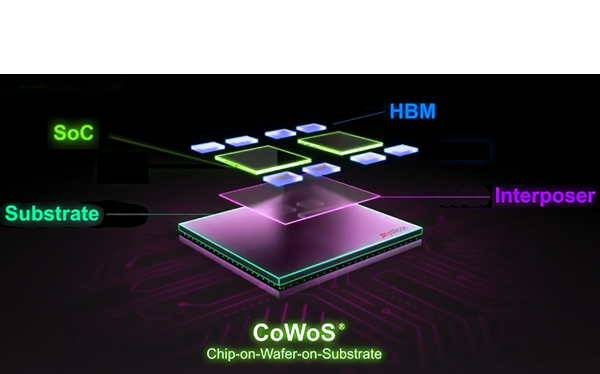

הטכנולוגיה הנפוצה ביותר בעולם היום היא הCoWoS של TSMC. השם CoWoS הוא קיצור של Chip on Wafer on Substrate ובגדול כשמה של הטכנולוגיה כן היא. TSMC ממקמת שבבים על גבי סיליקון נוסף, הנקרא Interposer, דרכו עוברת הקישוריות בין השבבים, ואת כל הטוב הזה ממקמת על מצע. לבסוף הכל נארז יחדיו ומתחבר אל הבורד. ראו תמונה.

עדיין קיימים קשיים -

אז האם זה הסוף? האם אפשר שוב לנשום לרווחה ולהכריז על תחייתו מחדש של חוק מור? בערך. הטכנולוגייה הזו מגיעה עם אתגרים קשים בפיתוח, בעיקר בתחום הבדיקות ופיזור החום. עוד המון פיתוח צריך להגיע מגזרת הקישוריות בין השבבים בתוך הצ'יפ (קיימים נסיונות לסטנדרטיזציה בecosystem ממספר מקומות אבל בפועל זה עוד לא פועל בצורה חלקה). נדרש המון ידע על מנת להצליח להפעיל כראוי שבבים הארוזים בצורה כזו וחברות העוזרות בקישוריות או במומחיות אחרת מוקמות בארץ ובחו"ל בדיוק בשביל להפוך את הטכנולוגיה לפשוטה להטמעה ולשימוש ככל האפשר. יחד עם זאת, אנחנו עוד לא שם.

מה צופן העתיד?

בעתיד חברות מבטיחות להשתמש בטכנולוגיה על מנת לערום את השבבים שלהן אחד על גבי השני, ולא רק אחד ליד השני. ישנם חברות שכבר עורמות זכרונות HBM אחד על גבי השני ואפילו שבבי לוגיקה ממש (ברודקום כבר הוציאה את הXPU האחרון עם מה שהיא קוראת לו טכנולוגיית 3.5D – ראו תמונה), אז, אחרי שמשנות ה60 האלקטרוניקה הלכה וקטנה משנה לשנה, היא צפויה ללכת ולגדול לרוחב ואפילו לגובה. יש למה לצפות.